[ad_1]

Actualizado a: 5 de octubre de 2023

Como sabrás, AMD también ha creado sus propios diseños de multinúcleo heterogéneo, como se ha hecho durante años en el mundo Arm o como también ha hecho más recientemente Intel con sus P-core y E-core. Sin embargo, la arquitectura híbrida de AMD es diferente a todo lo que hemos visto hasta ahora, y aquí te explicamos los motivos.

El multinúcleo heterogéneo ha llegado para resolver algunos problemas, pero no todos en el mundo x86

Primeramente decir que las CPUs con multinúcleo heterogéneos tienen algunas ventajas con respecto al multinúcleo convencional, como:

- Rendimiento mejorado: permiten que cada núcleo se especialice en tareas específicas, lo que puede mejorar el rendimiento general en comparación con una CPU homogénea. Por ejemplo, algunos núcleos pueden estar optimizados para tareas de cálculo intensivo, mientras que otros pueden ser más eficientes en el manejo de tareas de baja potencia.

- Eficiencia energética: al tener núcleos especializados, una CPU multinúcleo heterogénea puede ser más eficiente energéticamente. Esto significa que puede realizar tareas de menor consumo de energía en núcleos de baja potencia, lo que puede alargar la duración de la batería en dispositivos portátiles.

- Mejor manejo de cargas de trabajo variadas: relacionado con los dos puntos anteriores, hay que decir que dado que los núcleos heterogéneos pueden adaptarse a diferentes tipos de tareas, estas CPU son ideales para manejar cargas de trabajo variadas, según lo pesadas que sean, aplicando la tarea al núcleo más adecuado.

- Mejora de la multitarea: pueden permitir una mejor multitarea, ya que diferentes núcleos pueden encargarse de diferentes tareas simultáneamente, lo que mejora la capacidad de respuesta del sistema. Además, los núcleos eficientes suelen ser más pequeños, lo que permite integrar mayor cantidad de ellos en el mismo chip. Y no solo eso, también podría implementar más núcleos físicos y prescindir de los núcleos lógicos, es decir, del SMT o multihilo simultáneo, ya que esta tecnología puede generar muchas vulnerabilidades como hemos visto.

Por supuesto, también hay algunas desventajas en estos diseños, como:

- Complejidad de programación: la programación para CPUs multinúcleo heterogéneas puede ser más compleja que para CPUs homogéneas. Los desarrolladores deben ser capaces de aprovechar al máximo los diferentes tipos de núcleos y gestionar eficazmente la asignación de tareas a cada núcleo. Y, a nivel del planificador del sistema operativo (scheduler) también puede ser complejo para que funcione de forma correcta. Por otro lado, ten en cuenta que si los núcleos no cuentan con soporte para las mismas instrucciones, eso quiere decir que unos núcleos no pueden ejecutar cierto software, y se tiene que dejar para los que sí pueden.

- Compatibilidad y software: no todos los programas están optimizados para aprovechar los núcleos heterogéneos, lo que puede limitar el beneficio potencial en términos de rendimiento. Además, puede haber problemas de compatibilidad con software más antiguo.

- Coste y diseño de hardware: la implementación de una CPU multinúcleo heterogénea puede ser más costosa y complicada en términos de diseño de hardware en comparación con una CPU homogénea.

El caso x86

Lo anteriormente dicho se puede aplicar al ámbito de los procesadores Arm, como los SoCs para dispositivos móviles de Qualcomm, Samsung, MediaTeck, etc., así como los Apple, tanto los A-Series para dispositivos móviles como los M-Series para los ordenadores. Sin embargo, lo que hemos visto hasta el momento en el mundo x86, con Intel, no ha aprovechado del todo las ventajas del multinúcleo heterogéneo.

Me esto refiriendo a que los núcleos E-core de Intel, los de eficiencia, no soportan la tecnología HT, es decir, carecen de SMT. Pero los núcleos P-core sí que pueden procesar dos hilos simultáneamente por cada núcleo, por lo cual cada P-core se desdobla en dos núcleos lógicos. Por tanto, se evitan las posibles vulnerabilidades en los E-core, pero se sigue teniendo el riesgo en los P-core. Por tanto, una de las cosas que se han eliminado en el mundo Arm, no se ha hecho de igual modo en el mundo x86.

¿Habrá tomado nota AMD para mejorar esto en sus procesadores? Pues parece que no solo no han seguido el camino de Arm, sino que tampoco han seguido el camino de Intel. El caso de AMD es muy particular, y lo que han hecho es que tanto un tipo de núcleo como el otro sea compatible con SMT. Por tanto, tanto los núcleos grandes, Zen 4, como los núcleos pequeños, Zen 4c, se desdoblan en dos núcleos lógicos para ejecutar un thread cada uno de ellos.

AMD EPYC 9004 «Bergamo»: el primero en llegar

AMD lanzó el pasado junio de 2023 el procesador para el sector HPC y servidores, el EPYC 9004 «Bergamo». Este procesador cuenta con 128 núcleos y 256 threads. Pero la gran novedad de este microprocesador es que llega junto a una nueva y novedosa microarquitectura de CPU a la que han denominado Zen 4c. Es decir, no se trata de una nueva microarquitectura, sigue siendo una Zen 4, pero con algunos cambios como explicaré.

Se habían difundido muchos rumores sobre Zen 4c antes del lanzamiento, como que es una versión «lite» de Zen 4 con menos capacidad de procesamiento y, por lo tanto, un IPC más bajo, y que Zen 4c es la respuesta de AMD a las arquitecturas E-core de Intel, como «Gracemont» y «Crestmont». Resulta que no es ni una versión lite de Zen 4 ni algo parecido a un E-core, sino una implementación físicamente compacta del núcleo Zen 4, e idéntico en el resto de factores.

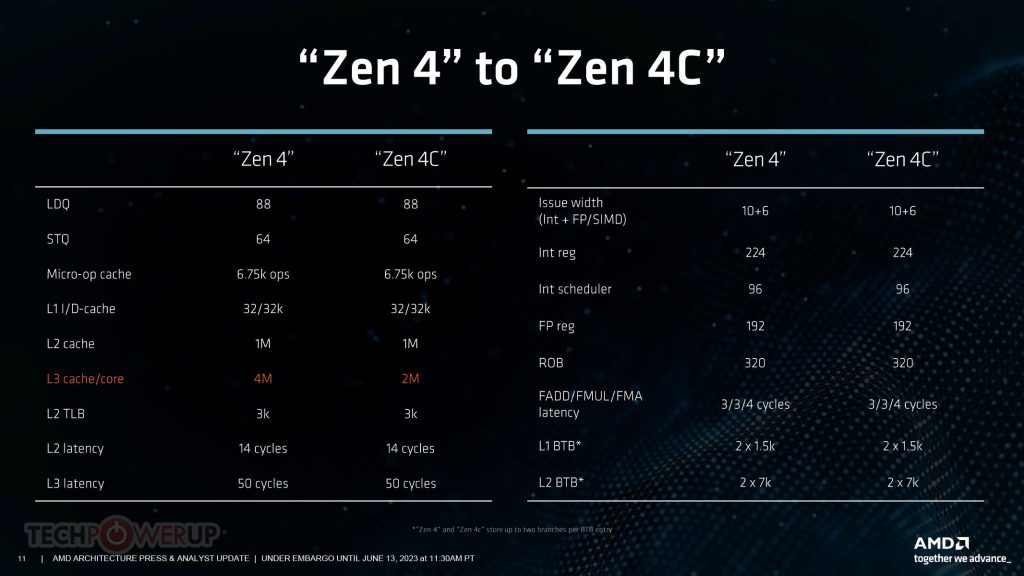

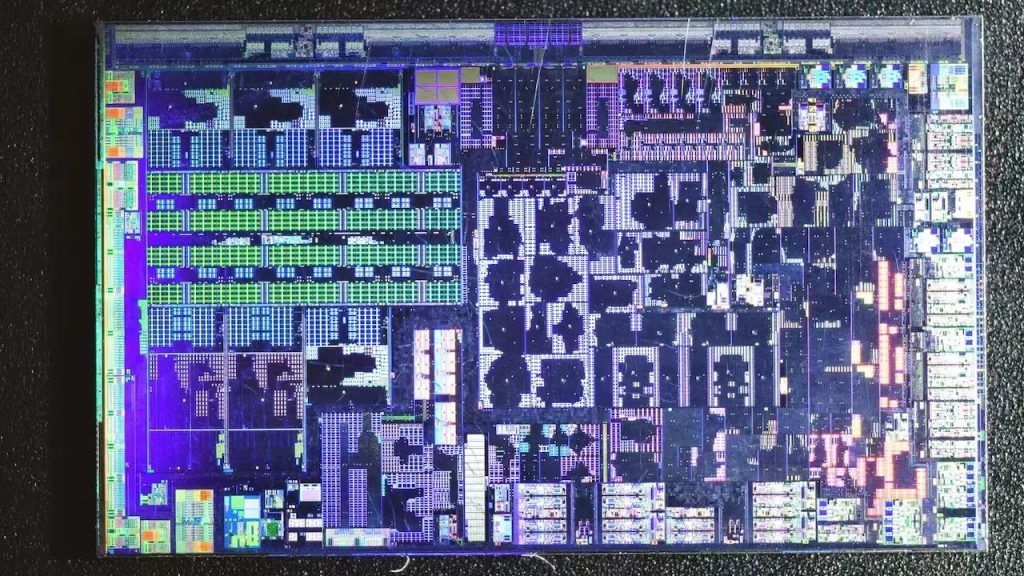

Lo primero que debemos destacar es que Zen 4c tiene el mismo IPC exacto que Zen 4. Es decir, si se comparasen dos núcleos a igual frecuencia de reloj, tanto el Zen 4 como el Zen 4c tendrían el mismo rendimiento IPC. Esto se debe a que su Front-End (la parte que trae, y decodifica las instrucciones), Back-End (unidades de ejecución), componente de L/S y jerarquía de caché interna son exactamente iguales.

Es decir, al analizar el Zen 4c, sorprendentemente nos encontramos que tiene la misma cola de carga 88-way, cola de almacenamiento 64-way, la misma caché de 675.000 microoperaciones, el mismo ancho de banda de ejecución de INT+FP de 10+6, el mismo archivo de registros INT exacto, el mismo planificador y las mismas latencias de caché. Las cachés L1I y L1D son del mismo tamaño que las de Zen 4, es decir, 32 KB, al igual que la caché L2 dedicada, que es de 1 MB. Lo único que ha cambiado es que la caché L3 efectiva por núcleo se ha reducido a 2 MB, en comparación con los 4 MB en el CCD de 8 núcleos de Zen 4.

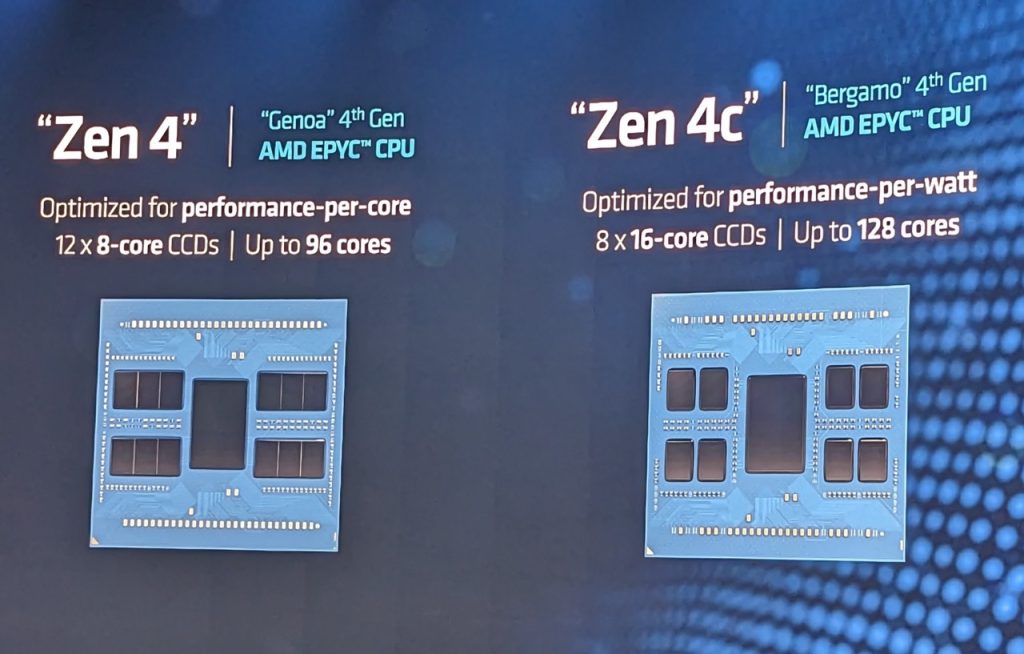

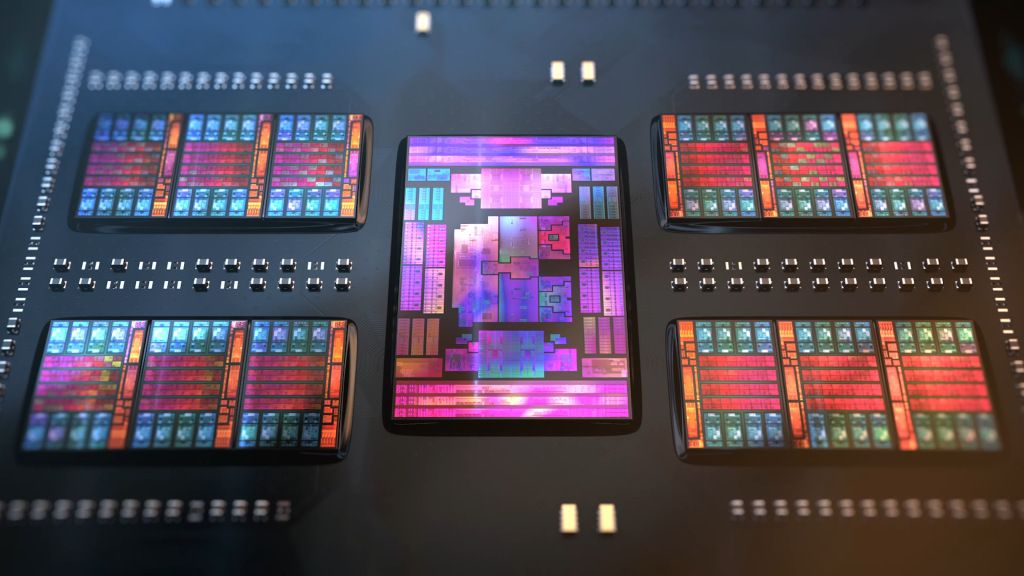

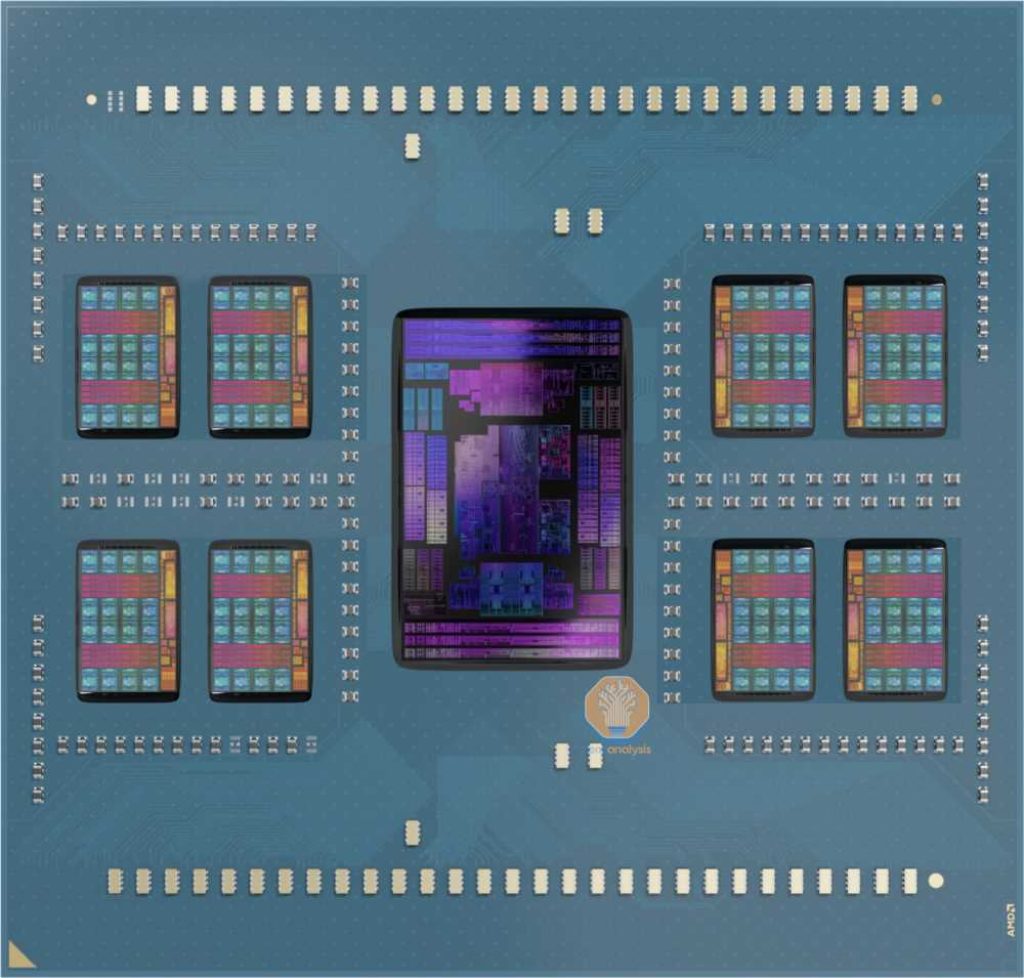

Mientras que el CCD de 8 núcleos regular de Zen 4 tiene ocho núcleos Zen 4 con una caché L3 de 32 MB, el nuevo CCD de 16 núcleos Zen 4c que AMD introdujo con «Bergamo» ve que el chiplet contiene dos CCX de 8 núcleos (complejos de núcleos de CPU), cada uno con 16 MB de caché L3 compartida entre los 8 núcleos del CCX. En este sentido, la organización de la caché de último nivel y del núcleo de la CPU en el CCD de Zen 4c tiene algunas similitudes con el CCD de Zen 2 (que usaba dos CCX de 4 núcleos). Pero, por lo demás, es como un Zen 4 convencional. Lo más interesante es que el CCD de 16 núcleos Zen 4c no es el primer producto de AMD de esta generación con una caché de último nivel más pequeña por núcleo. Para lo mismo en el proyecto Phoenix, es decir, la APU destinada a los equipos portátiles de la serie Ryzen 7040, que tienen 8 núcleos Zen 4 compartiendo una caché L3 de 16 MB.

Para cargas de trabajo de cálculo intensivo con un menor consumo de memoria, Zen 4c ofrece un rendimiento idéntico a Zen 4. Sin embargo, la caché L3 más pequeña debería afectar al rendimiento en cargas de trabajo sensibles al ancho de banda con conjuntos de datos grandes.

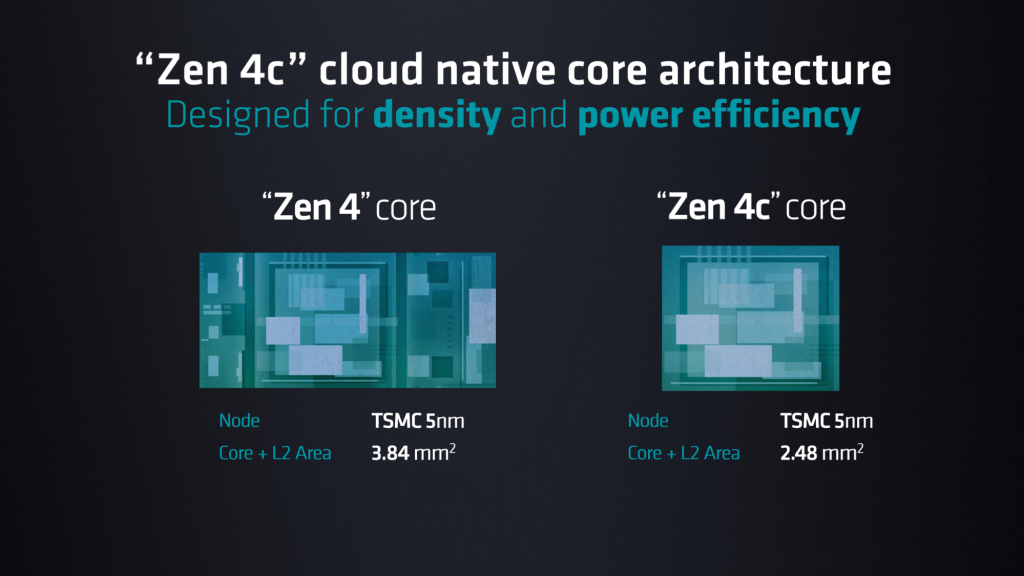

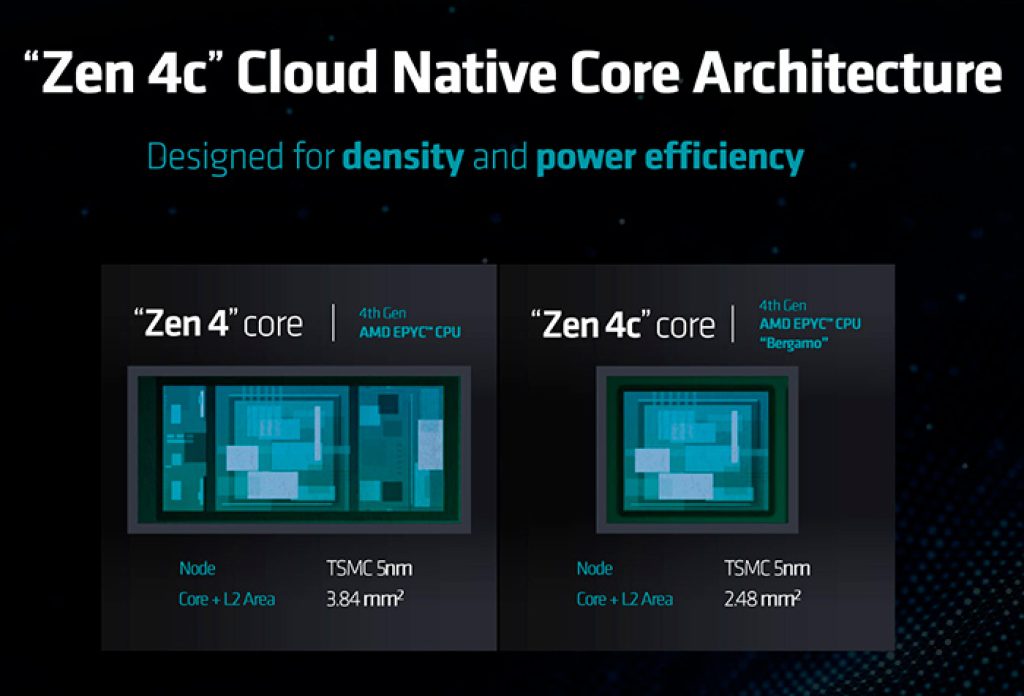

Y no, la minimización del tamaño del núcleo no proviene del nodo de fabricación, ya que el CCD de Zen 4c se construye en el mismo nodo TSMC de 5 nm EUV que utiliza la compañía para el CCD de Zen 4 de 8 núcleos regulares. Sin embargo, el núcleo de CPU Zen 4c es un 35% más pequeño que el núcleo Zen 4, con un área de matriz (por núcleo) de solo 2.48 mm², en comparación con 3.84 mm². ¿Es magia? ¿Cómo lo ha conseguido AMD?

Pues bien, los ahorros de tamaño en el núcleo probablemente provienen de la compactación de los diferentes componentes del núcleo sin reducir su forma o función de ninguna manera, es decir, una optimización en el diseño, routing y layout de estos núcleos. De este modo, con estos núcleos más optimizados, pero con idéntica ISA, soporte de extensiones de instrucciones, y SMT, se pueden integrar mayor cantidad de núcleos. Por ejemplo, el AMD EPYC 9004 «Bergamo» puede tener un recuento de 128 núcleos con CCDs de 16 núcleos Zen 4c. Mientras que el AMD EPYC 9004 «Genoa», basado en CCDs de 8 núcleos Zen 4, solo puede llegar a un recuento de 96 núcleos. ¡Impresionante!

AMD Zen 4c vs Intel E-core: diferencias

Intel ha estado vendiendo CPUs híbridas con una combinación de núcleos de alto rendimiento denominados P-core, como ya sabes, y núcleos E-core de alta eficiencia desde el lanzamiento de las CPUs Alder Lake de 12ª generación en noviembre de 2021. Esto es algo similar a los big.LITTLE de Arm, pero con diferencias como he dicho anteriormente, como que los P-core pueden tener tecnología HT o HyperThreading, además de soportar algunas instrucciones que los E-core no soportan, aunque parece que Intel dio marcha atrás con el tema de las AVX-512, y están desactivadas.

Ahora AMD ya tiene su propia versión de los núcleos eficientes. Pero AMD está haciendo las cosas de manera diferente, muy diferente de hecho. Anteriormente, he explicado cómo los núcleos Zen 4c más pequeños de AMD son funcionalmente idénticos a los núcleos Zen 4 completos, con la excepción de ofrecer la mitad de la caché L3. Y, sin embargo, de alguna manera ocupan solo la mitad del espacio de un núcleo Zen 4, y no todo se debe a esa disminución de caché, sino algo más. Es decir, recompilando, los núcleos Zen 4c ejecutan las mismas instrucciones que Zen 4 y también cuentan con SMT, cosa que los E-core de Intel no.

Todo se reduce a los objetivos de diseño físico, como he comentado, una optimización a varios niveles que da como resultado esta reducción de tamaño. Además, hay que tener en cuenta que mientras el Zen 4 puede admitir frecuencias de operación de hasta 5.5 GHz y más allá, en el caso del Zen 4c, el objetivo de velocidad de reloj se redujo a la región de 3 GHz. Resulta que eso marca una gran diferencia en cómo se diseña un núcleo de CPU. Con velocidades de reloj más bajas, se pueden hacer las estructuras internas mucho más pequeñas sin preocuparse por la interferencia y las pérdidas de energía que vienen con frecuencias de operación elevadas. Aquí es donde está la clave.

Mientras que Intel lo que ha hecho es desarrollar una microarquitectura para sus P-core y otra diferente para sus E-Core. Las E-core heredan parte del camino que Intel había marcado con los Intel Atom, que fueron en un inicio núcleos con ejecución en orden, pero en sus últimos diseños pasaron a ser núcleos con ejecución fuera de orden (OoOE). Por tanto, la reducción de tamaño y de consumo proviene de la propia arquitectura, siendo un núcleo con menor rendimiento, distinto IPC.

Por otro lado, mientras que los núcleos E-core de Intel tienen un tamaño bastante más pequeño en comparación de los P-core, la diferencia entre un Zen 4 y un Zen 4c quizás no es tan llamativa como en el caso de Intel, en el que un núcleo P tiene unas dimensiones similares a 4 núcleos E. No obstante, esta diferencia entre los núcleos heterogéneos de Intel también hace que la gestión de asignación de cargas de trabajo y el equilibrio de carga sea bastante más complicado que en el AMD.

AMD Ryzen «Phoenix 2»: la APU con Zen 4 + Zen 4c

AMD no solo ha usado esta Zen 4c para los EPYC para los equipos de alto rendimiento, también la ha anunciado para usarse en APUs para equipos portátiles, y la ha llamado con el nombre clave Phoenix 2, es decir, una segunda versión de la Phoenix 1 basada en Zen 4. Estos núcleos se usarán, entre otros productos, en el Ryzen 3 7440U.

Las especificaciones técnicas de Phoenix 2, en comparación con Phoenix 1, son las siguientes:

| SOC | Phoenix 2 | Phoenix 1 |

|---|---|---|

| Nodo o proceso de fabricación | 4nm | 4nm |

| Tamaño del die | 137mm2 | 178mm2 |

| Recuento de transistores | — | — |

| Microarquitectura | Zen 4 + Zen 4C | Zen 4 |

| Cores / Threads | 8/16 o 6 / 12 (con dos núcleos desactivados) | 8 / 16 |

| Frecuencia de reloj máxima | 4.7 GHz | 5.1 GHz |

| Arquitectura de GPU | RDNA 3 | RDNA 3 |

| GPU Compute Units | 4 CUs (256 SPs) | 12 (768) |

| Frecuencia de reloj de la GPU | 2500 MHz | 2800 MHz |

| Memoria soportada | LPDDR5-6400 LPDDR5X-7500 |

DDR5-5600 LPDDR5x-7500 |

| TDP | 15-30W | 15-30W |

| Productos a los que va destinado | Handhelds | Laptops / Handhelds |

| Fecha de lanzamiento | 2024 | 2024 |

Como se puede apreciar, Phoenix 2 con núcleos híbridos, será destinada a equipos de menor consumo, dentro de los portátiles. De los núcleos en la versión confirmada, la de 6 núcleos, se contará con 2 núcleos Zen 4 y 4 núcleos Zen 4c. Esta estrategia de ofrecer dos APUs diferentes es algo extraña, pero veremos habrá que esperar a ver qué aparece finalmente en el mercado, pero podría haber sorpresas…

Conclusión

Aunque AMD sigue usando SMT, pudiendo esto dar posibilidad a ciertas vulnerabilidades, desdoblando cada núcleo físico en dos núcleos lógicos para que cada uno se encargue de un thread o hilo simultáneamente, pero también es verdad que ha acertado en el diseño en lo que Intel no ha sabido solventar, como la problemática de la asignación de cargas al ser núcleos tan diferentes.

‘Con Zen 4/Zen 4c, AMD está marcando un cambio significativo desde su diseño uniforme de núcleos y adoptando un futuro en el que la combinación de diferentes variaciones de núcleos de CPU debería proporcionar una ventaja competitiva frente a la arquitectura multinúcleo heterogéneo de la competencia (Arm en general, Apple, e Intel). Al utilizar la misma microarquitectura para ambos tipos de núcleos de CPU, AMD podría ofrecer ventajas adicionales, como una mejor compatibilidad y una reducción de la fragmentación en el desarrollo de aplicaciones/controladores.’Con Zen 4/Zen 4c, AMD está marcando un cambio significativo desde su diseño uniforme de núcleos y adoptando un futuro en el que la combinación de diferentes variaciones de núcleos de CPU debería proporcionar una ventaja competitiva frente a la arquitectura multinúcleo heterogéneo de la competencia (Arm en general, Apple, e Intel). Al utilizar la misma microarquitectura para ambos tipos de núcleos de CPU, AMD podría ofrecer ventajas adicionales, como una mejor compatibilidad y una reducción de la fragmentación en el desarrollo de aplicaciones/controladores.

¡Ojito, porque AMD ha sido la última en llegar y podría haber dado con la clave! Seguiremos muy de cerca estos chips…

[ad_2]

Source link